Product Summary

The TPS51116RGER provides a complete power supply for both DDR/SSTL-2 and DDR2/SSTL-18 memory sys- tems. It integrates a synchronous buck controller with a 3-A sink/source tracking linear regulator and buffered low noise reference. The TPS51116RGER offers the lowest total solution cost in systems where space is at a premium. The TPS51116RGER synchronous control- ler runs fixed 400kHz pseudo-constant frequency PWM with an adaptive on-time control that can be configured in D-CAP(TM) Mode for ease of use and fastest transient response or in current mode to support ceramic output capacitors. The 3-A sink/source LDO maintains fast transient response only requiring 20-μF (2 × 10 μF) of ceramic output capacitance. In addition, the LDO supply input is available externally to significantly reduce the total power losses. The TPS51116RGER supports all of the sleep state controls placing VTT at high-Z in S3 (suspend to RAM) and discharging VDDQ, VTT and VTTREF (soft-off) in S4/S5 (suspend to disk). It has all of the protection features including thermal shutdown and is in a 20-pin HTSSOP PowerPAD(TM) package.

Parametrics

Absolute maximum ratings: (1)VIN, Input voltage range: VBST: -0.3 to 36 V; VBST wrt LL: -0.3 to 6v; CS, MODE, S3, S5, VTTSNS, VDDQSNS, V5IN, VLDOIN, VDDQSET: -0.3 to 6v; PGND, VTTGND: -0.3 to 0.3 v; (2)VOUT Output voltage range, DRVH: -1.0 to 36 V; LL: -1.0 to 30v; COMP, DRVL, PGOOD, VTT, VTTREF: -0.3 to 6v; (3)TA, Operating ambient temperature range: -40 to 85 °C; (4)Tstg, Storage temperature: -55 to 150 °C.

Features

Features: (1)Synchronous Buck Controller (VDDQ): Wide-Input Voltage Range: 3.0-V to 28-V; D–CAP(TM) Mode with 100-ns Load Step Re-sponse; Current Mode Option Supports Ceramic Output Capacitors; Supports Soft-Off in S4/S5 States; Current Sensing from RDS(on) or Resistor; 2.5-V (DDR), 1.8-V (DDR2) or Adjustable Output (1.5-V to 3.0-V); Equipped with Powergood, Overvoltage Pro- tection and Undervoltage Protection.; (2)3-A LDO (VTT), Buffered Reference (VREF): Capable to Sink and Source 3 A; LDO Input Available to Optimize Power Losses; Requires only 20-μF Ceramic Output Ca-pacitor; Buffered Low Noise 10-mA Output; Accuracy ±20 mV for both VREF and VTT; Supports High-Z in S3 and Soft-Off in S4/S5; Thermal Shutdown.

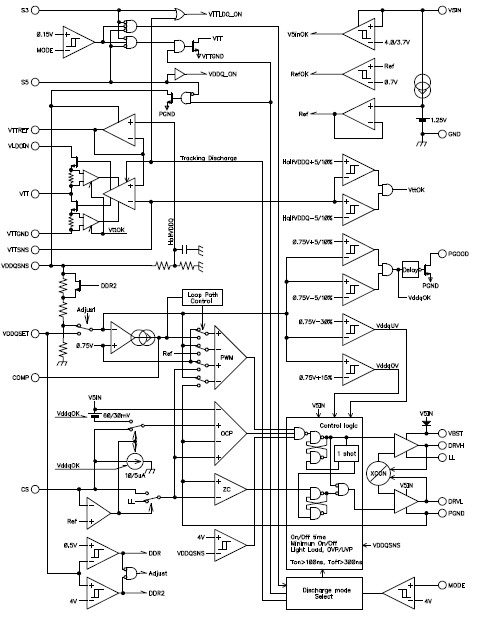

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

TPS51116RGER |

Texas Instruments |

DC/DC Switching Controllers DDR2 SWITCHER AND LDO |

Data Sheet |

|

|

||||||||||||

|

TPS51116RGERG4 |

Texas Instruments |

DC/DC Switching Controllers DDR2 SWITCHER AND LDO |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))