Product Summary

The 74HC132PW is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL). It is specified in compliance with JEDEC standard no. 7A. The 74HC132PW contains four 2-input NAND gates which accept standard input signals. 74HC132PW is capable of transforming slowly changing input signals into sharply defined, jitter-free output signals. The gate switches at different points for positive and negative-going signals. The difference between the positive voltage VT+ and the negative voltage VT- is defined as the hysteresis voltage VH.

Parametrics

74HC132PW absolute maximum ratings: (1)tPHL/ tPLH propagation delay nA, nB to nY CL = 15 pF; VCC = 5 V: 11 ns; (2)CI input capacitance: 3.5pF; (3)CPD power dissipation capacitance per gate: 24 pF.

Features

74HC132PW features: (1)Output capability: standard; (2)ICC category: SSI.

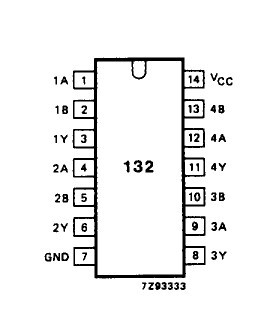

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74HC132PW,112 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2IN NAND SCHMIT |

Data Sheet |

|

|

||||||||||||

|

74HC132PW,118 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND SCHMITT TRIG |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))